在芯片技术逐渐逼近物理极限的当下,科学家们将目光投向了一种如同“薄如蝉翼”般的新材料——原子级二维半导体,像仅有三个原子厚的二硫化钼(MoS₂)。从理论层面来讲,它们能够使晶体管变得更小、运行速度更快且更加节能,是延续摩尔定律的关键所在。然而,现实却不尽人意——这些超薄材料一旦放置在传统硅基底之上,其性能便会大打折扣,电子运行速度缓慢且紊乱,远远无法达到预期效果。

如今,一项由麻省理工学院(MIT)与韩国成均馆大学携手合作的新研究,找到了一个出人意料的解决办法:并非添加更多材料,而是主动制造“空”。他们发现,在二维半导体与底层电路之间留出一层仅有几纳米厚的真空缝隙,就能让电子迁移率提升近10倍,这就如同给芯片装上了“隐形涡轮增压”。

这个想法听起来颇为简单,甚至有些反直觉——毕竟工程师们耗费数十年追求的是“紧密贴合”,为何现在反而要“留缝”呢?但问题恰恰就出在这“贴合”上。在传统芯片中,半导体薄膜是直接生长或转移在二氧化硅等绝缘层上的。而这些基底表面布满了微观缺陷、电荷陷阱以及晶格振动(声子),恰似一条坑洼不平的土路。当半导体薄至原子级别时,整个材料几乎完全暴露于这些干扰之中,电子每前进一步都会被“绊倒”,进而导致速度减缓、发热加剧、信号减弱。

新方法的核心要点在于让二维材料“悬空”。研究团队研发出了一种精妙的微纳加工工艺:首先在硅片上涂抹一层可溶性聚合物作为“临时支架”,接着在其上面精确放置二硫化钼薄膜;随后使用温和溶剂将聚合物清洗掉,仅留下一层极薄的空气(或真空)间隙,以此将半导体与下方结构分隔开来。这层空隙虽然微小(约5–10纳米),但其意义却极为重大——因为空气几乎是电学“透明”的:不存在杂质、没有声子散射、也没有电荷噪声。电子在悬空的通道中奔跑,就如同在无风的高速公路上疾驰。

实验结果振奋人心:经过处理后的二硫化钼晶体管,电子迁移率从不足30 cm²/V·s跃升至280 cm²/V·s,已接近商用硅材料的水平;同时,开关电流比提高了两个数量级,漏电流也显著降低。这意味着器件能够在更低电压(低至0.5伏)下稳定运行,功耗大幅下降——对于手机、智能手表、植入式医疗设备等依靠电池供电的设备而言,这无疑是一项具有革命性的进步。

更为关键的是,这项技术与现有的芯片制造流程相互兼容。所使用的牺牲层材料是标准光刻胶,清洗步骤也早已在生产线上成熟应用。研究团队表示,无需采用昂贵的新材料或全新设备,只需对几道工序进行调整,就能实现性能的飞跃。

当然,挑战依旧存在。大面积的悬空结构可能在机械方面较为脆弱,其在长期使用过程中是否会发生变形或塌陷仍有待验证。为此,团队已经设计出了微米级“支撑柱”阵列,在保证大部分区域悬空的同时提供局部锚点,从而兼顾性能与可靠性。

这项突破的意义远不止于性能的提升。它揭示了一个深层次的原理:在纳米尺度下,环境干扰往往比材料本身对性能的限制更为严重。与其持续提纯材料,不如优化其“生存空间”。未来,这一“空气衬底”策略还能够应用于石墨烯、黑磷、氮化硼等其他二维材料,推动柔性电子、超快光电探测器乃至量子器件的发展。

从“填满每一寸”到“聪明地留白”,这场由“空”引发的变革提醒着我们:有时候,真正的创新并非是堆砌更多,而是懂得何时放手——给电子一片自由的空间,它们自会跑出未来的速度。

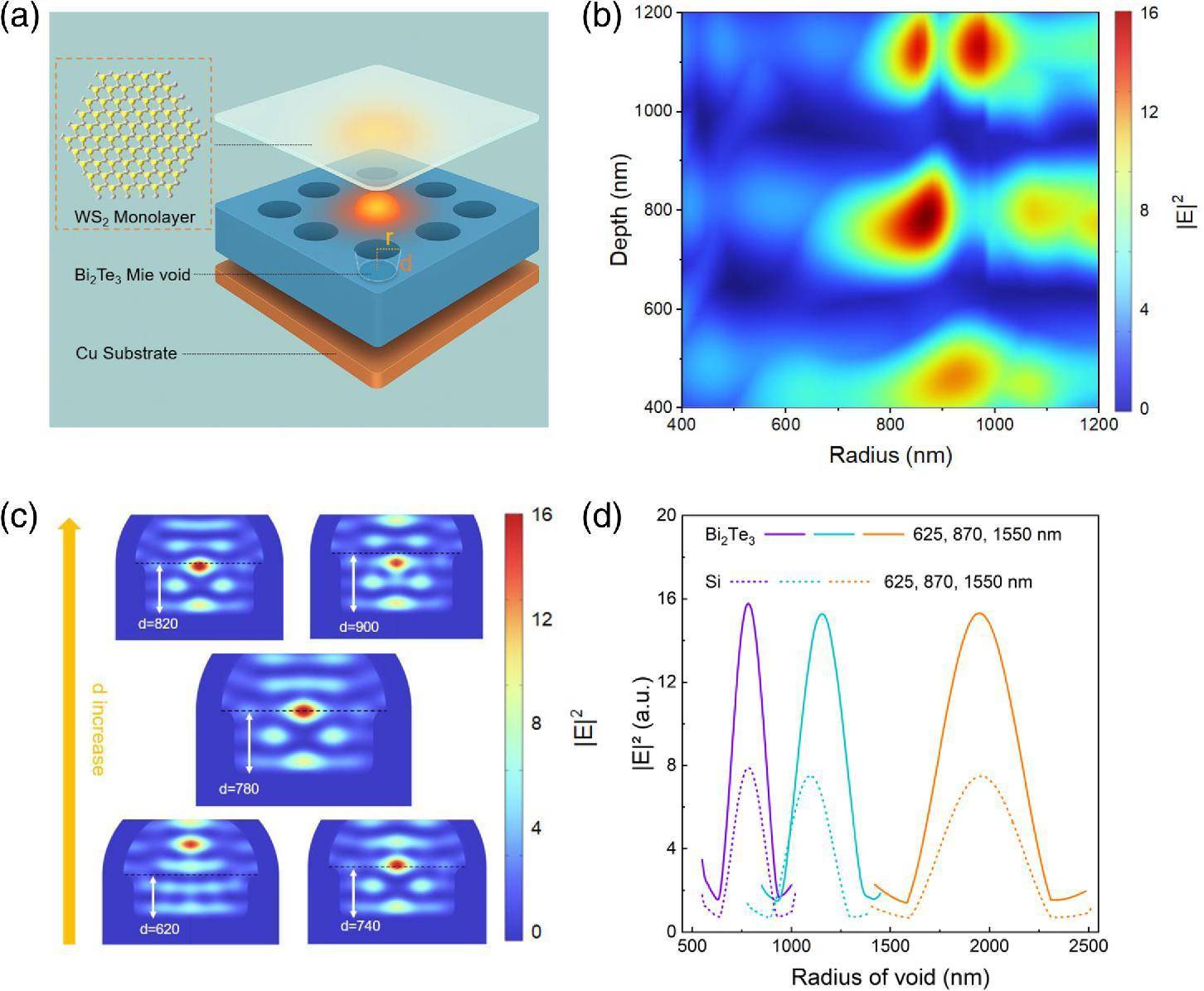

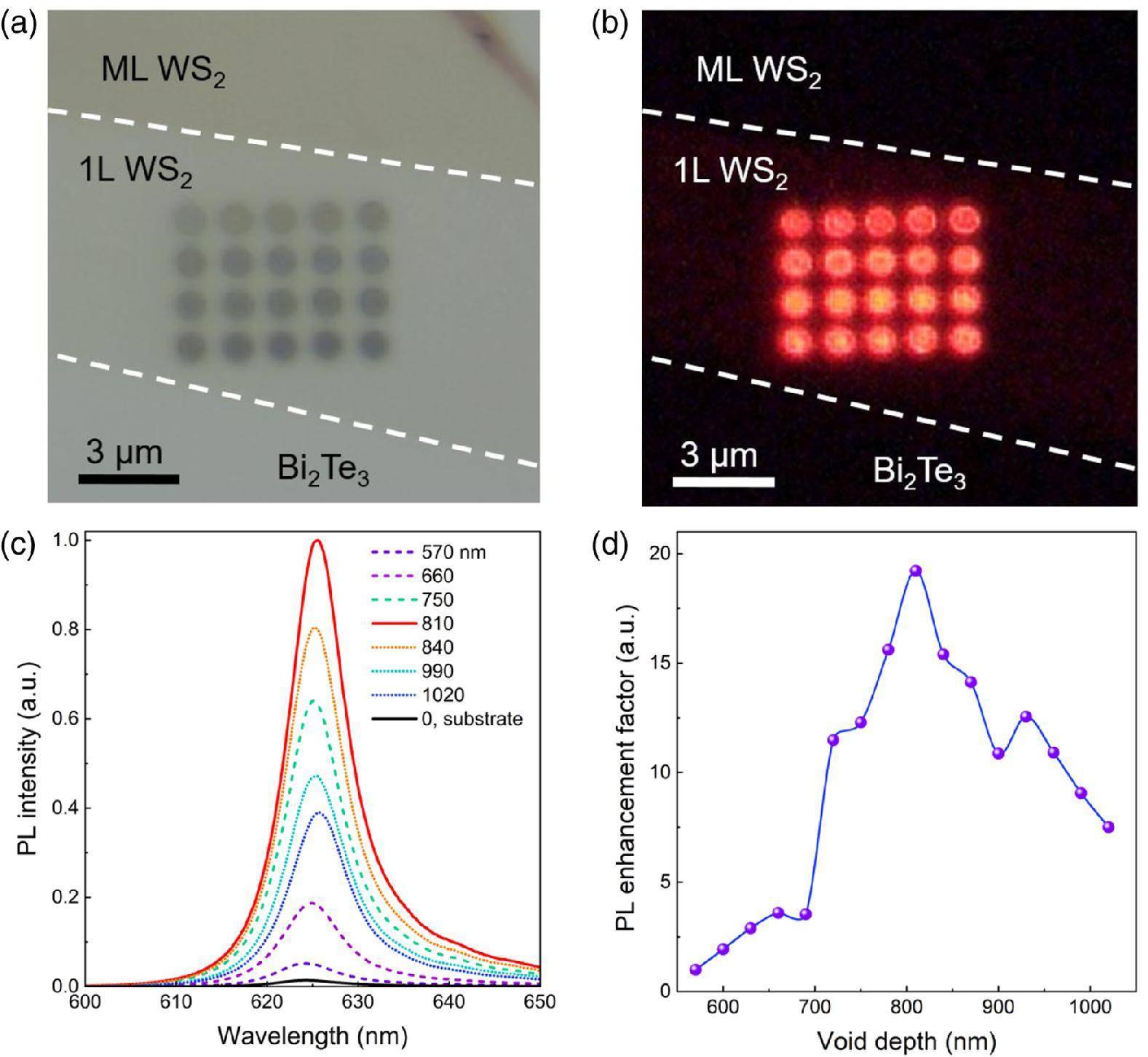

参考资料:“Light–matter interaction in van der Waals heterostructures with Mie voids” by Zhuoyuan Lu, Kirill L. Koshelev, Pavel Tonkaev, Ziyu Chen, Dawei Liu, Wenkai Yang, Yuri Kivshar and Yuerui Lu, 14 February 2026, Advanced Photonics. DOI: 10.1117/1.AP.8.2.026002

#芯片技术 #二维半导体 #电子迁移率 #微纳加工工艺北港网提示:文章来自网络,不代表本站观点。